现在的位置:主页 > 期刊导读 >

基于FPGA和AD9226的高速交叉采样设计

【作者】网站采编【关键词】【摘要】1 引言 高速且高分辨率的信号采集技术在雷达、天文和气象等方面有着广泛的应用,然而要达到高速和高分辨率,则必须对信号进行高速率的采样。但是采样速率与设计成本和设计难度

1 引言

高速且高分辨率的信号采集技术在雷达、天文和气象等方面有着广泛的应用,然而要达到高速和高分辨率,则必须对信号进行高速率的采样。但是采样速率与设计成本和设计难度之间有着巨大的矛盾,往往随着采样速率的提高,设计成本升高,设计难度增加。交叉采样很好地解决了这一问题,利用FPGA产生等相位差的时钟控制信号,使用多片芯片在原采样周期内交叉采样,相当于原采样周期的采样个数增加,从而使得整体采样速率得以提升。本设计方案用三片AD9226进行高速交叉采样,使原本65MHz的采样速率提高到195MHz。

2 原理分析

2.1AD9226采样原理

AD9226采用单一的时钟信号来控制内部所有的转换,ADC采样是在时钟的上升沿完成。AD9226采用带有误差校正逻辑的多级差分流水结构,在65Msps的转换速率下,采样时钟的占空比应保持在45%~55%之间;在低电平期间,输入处于采样状态;高电平期间,输入处于保持状态。图1为其采样时序图,从图中可以看出:由于AD9226采用的多级流水结构,其在每个时钟周期的上升沿捕获一个采样,八个周期以后才可以输出转换结果。图中TOD为数据延迟时间,最小值为3.5ns,最大值为7ns。

图1ADC采样时序图

图2 三路交叉采样原理图

2.2 交叉采样原理

交叉采样原理基于使用多片相对低速的并行ADC实现高速数据采集。n路ADC中每一片ADC的采样频率是整个系统采样频率的1/n,通过算法调整可使每一路通道时钟具有固定相位差,采样数据经多路排序合并后,可达到一路ADC采样速率n倍的效果。根据AD9226的特性和交叉采样原理,可绘制出三路交叉采样原理图,如图2所示,理想条件下各路时钟相位依次相差120°,每一路时钟信号的占空比为50%,满足AD9226的采样时钟要求。

中国水利:2013年,在大规模水利建设全面展开、安全生产任务繁重的情况下,水利安全生产形势继续保持总体稳定。在这方面,采取了哪些措施?

2.3 正弦波信号采样

当通过ADC采集到数据后要传输到DAC对所采样的正弦波信号进行还原,采样方式采用顺序采样,必须保证采样点数与还原点数相同,即ADC采样时钟与DAC工作时钟保持一致,根据采样定理可以直接有效地证明ADC的采样速率。但由于ADC和DAC的转换都需要时间,因此还原波形相对于原波形会产生一定的相位差。

图4 三路交叉采样FPGA原理图

图5 三路交叉采样时序仿真图

3 FPGA模块设计

3.1 单路采样设计

保险公司的业务流程通常分为三个环节,包括接受投保人申请、收取投保人保费、发生承保事件的前期调查取证以及对受益人进行赔付等多个环节,每个环节都有可能产生一定的财务风险。

3.2 三路交叉采样设计

三路交叉采样FPGA原理图如图4所示,由时序控制、延时、单路采样、数据处理四个模块组成,其中时序控制模块用来产生三路ADC交叉采样所需要的采样时钟,延时模块用来产生数据采集时钟,三个单路采样模块用来接收三路采样数据,数据处理模块负责把三路数据转成单路输出。

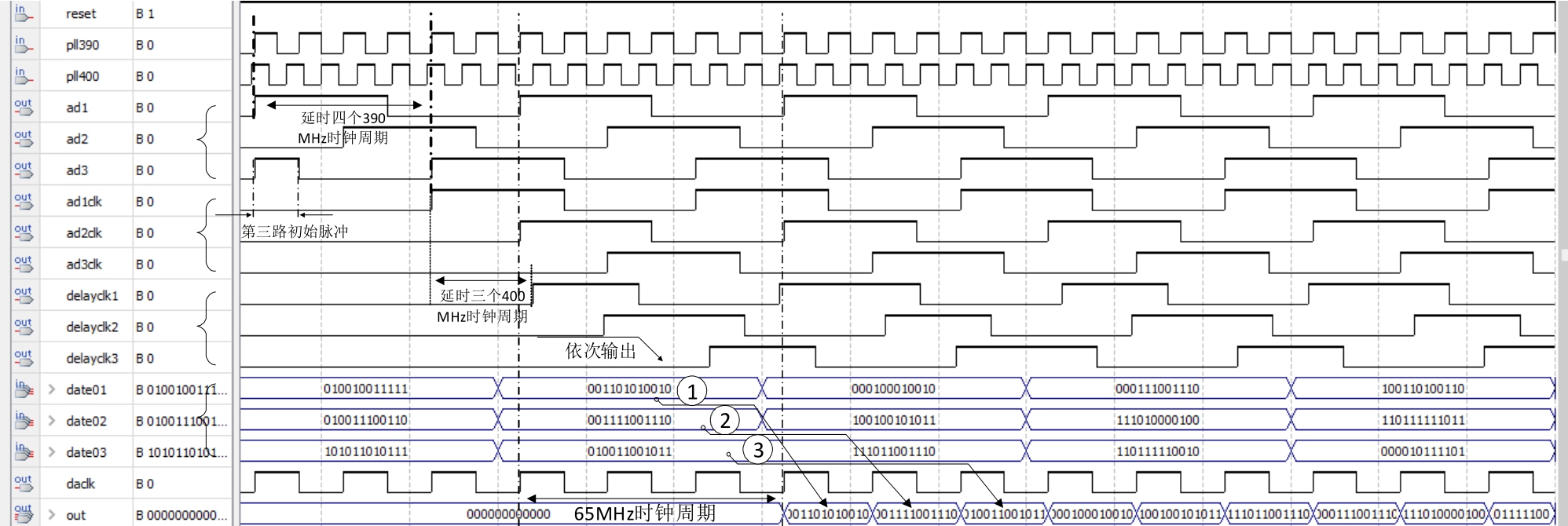

三路交叉采样时序仿真图如图5所示,其中“reset”表示复位时钟,“pll390”表示390MHz时钟,“pll400”表示400MHz时钟,“ad1、ad2、ad3”表示初始三路交叉采样时钟,“ad1clk、ad2clk、ad3clk”表示校正后三路交叉采样时钟,“delayclk1、delayclk 2、delayclk 3”表示数据采集时钟,“daclk”表示数模转换器AD9764工作时钟,“date01、date02、date03”表示三路65MHz采样数据,“out”表示单路195MHz采样数据输出。

3.2.3 单路数据采集

根据三路交叉采样原理和AD9226的特性首先要生成三路相位差为120°、占空比为50%的65MHzADC采样时钟,其实现方法是使用PLL IP核对50MHz时钟信号倍频产生390MHz的时钟,并生成用于延时的400 MHz时钟,然后对390MHz的时钟进行六分频,在分频的六个时钟周期内,将第一路的高低电平依次设置为“111000”,第二路设置为“001110”,第三路设置为“100011”。并同时对390MHz的时钟进行2分频输出195MHz的DAC工作时钟。

本论文受“基于GDP导师团队指导模式下的研究生培养研究与实践(JG2016YYB03)”、“燃气轮机动力装置虚拟性能仿真实验”、“燃气轮机发电机组半物理仿真实验教学系统”等教学改革项目资助完成。

近年来,智能手机在中国的普及以及互联网的发展,助推了表情包经济的发展。腾讯公司此前发布报告称,今年春节后,微信月活跃账户超过10亿。实际上,在表情包诞生之初,表情包并没有一个明晰的盈利模式,几乎所有表情包都是免费的。即便某些使用者通过社交软件“打赏”给表情包开发者,也只是“杯水车薪”。对于手机用户来说,他们绝大多数在使用聊天工具时都会使用表情包。作为简单、有含义的表达方式,表情包承担了文字之外的情感表达。庞大的用户群是表情包衍生品的潜在客户。目前,在淘宝上,与表情包相关的商品有近40万件,覆盖了玩具、数码、家具、衣服等众多类目商品。

单路采样FPGA原理图如图3所示,PLL400M60M产生60 MHz ADC的采样时钟和用于延时的400 MHz倍频时钟,延时模块负责把输入的采样时钟延时后得到数据采集时钟,数据处理模块完成对数据的采集,并将采集到的采样数据传输到数模转换器AD9764对所采样的正弦波信号进行还原。

由于在得到采样数据后,要输出到数模转换器AD9764对所采样的波形进行还原,为了避免采样点数与还原点数不一致而带来的误差,就必须保证ADC采样时钟与DAC工作时钟一致。因此进行单路数据采样时,在检测到数据采集时钟的上升沿时先将采样数据暂存起来,在检测到校正后采样时钟的上升沿后将采样数据输出,虽然采样数据的输出会有一个65MHz时钟周期的延迟,但是可以保证ADC采样时钟与DAC工作时钟一致,避免误差的产生。

AD9226数据延迟时间,最小值为3.5ns,最大值为7ns,当每一路的数据采集时钟相对于采样时钟延时大于7ns时,可以保证采样数据的准确性,400MHz的时钟的周期为2.5ns,延时三个400MHz时钟周期可以到达要求。如图5所示,三路“delayclk”相对于“adclk”有三个400MHz时钟周期的延时。

3.2.1 采样时钟设计

交叉采样时序仿真图如图5所示,“ad1、ad2、ad3”三路等相位差输出,满足上述要求,但“ad1”与“ad3”在初始时刻都有脉冲产生,会使得第一路和第三路同时开始采样,导致交叉采样在数据输出时会产生混乱,故需要消去“ad3”的初始脉冲。其实现方法是分别用两个计数器对输入信号的高电平和低电平的持续时间(脉宽)进行计数(在时间上是同时但独立计数),只有当高电平脉宽计数大于2时,判为遇到正确信号,输出为“1”;若低电平脉宽计数大于2时,输出为“0”。“ad3”的初始高电平脉宽计数为1,判为遇到错误信号,无法输出初始脉冲,如图5中的“ad3clk”所示。由于FPGA是多进程并行运行,在消除第三路初始脉冲的进程中对脉冲进行检测时,会有一个390MHz时钟周期的延时。同理,检测计数次数与计数是并行运行的,也会有一个390MHz时钟周期的延时,故“adclk”时钟输出相对于“ad”时钟会有四个390MHz时钟周期的延时。

利用红外线成像仪测试,土墙日光温室散热有热桥存在[2],主要是导热体的砼圈梁前坎,其次是后坡与前棚之间、后坡与侧墙之间的缝隙,造成温室密闭性不够,导致气体存在贯流散热。三是后坡结构简单,厚度不足,隔热保温能力差,四是散热面最大的为前棚面上的保温被,其质量好坏直接影响着温室的温度。彩钢后屋面主要是彩钢和墙体的缝隙,使用后,形成的彩钢板之间的缝隙,造成大量散热,以及聚苯板容重小,厚度不足,隔热性能达不到要求。

3.2.2 采样误差校正

3.2.4 高速数据处理

在完成三路65MHz数据采集后,要实现单路195MHz采样数据输出,其解决思路与交叉采样的思路一致,交叉采样是使用三片AD9226在65MHz的时钟周期内依次采样,三路转单路数据输出则可以在65MHz的时钟周期内依次输出采样数据。其实现方法是对195MHz时钟进行三分频,在分频的三个时钟周期内按照采样顺序依次输出采样数据,如图5所示,上一个65MHz时钟周期内的三路采样数据(即“date01、date02、date03”)在下一个时钟周期由单路(即“out”)依次输出。

在xoy平面上沿整数格点按一定步伐行走的路径统称为格路。Dyck路是格路的一种,由于在有序分拆、无序分拆、恒等式的组合证明、RNA第二结构等研究中有广泛的应用,受到众多研究者的重视,对各种有限制条件的格路计数一直是组合数学中一个热门的研究课题。

AD9226模数转换后的采样数据输出高低位相反,因此FPGA分配采样数据的输入引脚时,高低位顺序应当相反。AD9226的采样数据是12位,而模数转换器AD9764的采样数据是14位,所以需要将12位采样数据左移两位,在低位进行补零,相当于采样数据乘以4。之所以在低位后面进行补零,是为了防止高位补零后模数转换器输出的电压幅度过小,而使波形无法还原。

3.3 195MHz采样频率验证

根据采样定理可以验证采样频率,但数模转换器AD9764的工作频率最高位125MHz,195MHz的采样频率无法直接验证,但可以通过间接的方法对采样频率进行验证。先对单路AD9226进行60MHz采样频率测试,观察其是否能够还原30MHz正弦波信号,由此来验证单路采样的正确性。然后进行交叉采样测试,先进行60MHz的采样频率测试,观察其采样结果是否与单路60MHz采样结果相同,可验证交叉采样的正确性。再进行90MHz采样频率的测试,观察其是否能够还原45MHz正弦信号波形,可进一步验证交叉采样。单路测试和交叉采样的正确性即可验证195MHz采样频率的正确性。

4 测试结果

4.1 误差测试

给予120MHz的采样时钟对1MHz的正弦波信号进行误差校正前采样测试和误差校正后采样测试,在示波器界面上方显示采样还原后的波形,下方显示原波形,右下角显示原波形频率,如表1所示,误差校正前的还原波形会产生明显的毛刺,当误差校正后的还原波形得到明显改善。

4.2 单路采样测试

先对第一路ADC进行采样测试,60MHz采样时钟分别对1MHz、30MHz、32MHz正弦波信号进行采样,单路采样结果如表2所示,低于30MHz的正弦波信号还可以被失真较小地还原。超过30MHz后,还原波形失真严重,符合采样定理,由此可验证第一路ADC采样的正确性。然后变换输入端口对第二路、第三路分别进行测试,与第一路结果相同,由此可验证三路ADC采样均正确。

4.3 交叉采样测试

首先用60MHz的采样时钟分别对1MHz、30MHz、32MHz的正弦波信号进行采样,测试结果如表3所示,低于30MHz的正弦波信号还可以被失真较小地还原,超过30MHz后,还原波形严重失真,符合采样定理,与单路采样结果相同,可验证交叉采样的正确性。更高采样频率验证,90MHz的采样时钟分别对1MHz、45MHz、47MHz的正弦波信号进行采样,测试结果如表3所示,低于45MHz的正弦波信号还可以被失真较小地还原,超过45MHz后,还原波形严重失真,符合采样定理。单路测试和交叉采样的正确性即可验证195MHz采样频率的正确性。

表1 误差校正效果对比

images/BZ_12_530_1136_1994_1574.png

表260MHz单路采样波形

采样频率6060MHz还原波形信号频率1MHz 3030 M H z 3232 M H z

表360MHz、90MHz交叉采样波形

采样频率6060 M H z还原波形信号频率信号频率采样频率3232 M H z 1010 M H z 3030 M H z还原波形9090 M H z 1 M H z 4545 M H z 4747 M H z

5 结论

针对三通道模数转换器AD9226的高速交叉采样设计中的误差,本设计从两方面给予改进:通过消除第三路的初始脉冲,避免了由于第一路和第三路同时采样所导致的采样数据输出混乱;通过把校正后采样时钟和数据采集时钟分离,避免了AD9226数据延迟时间导致的误差。测试结果表明,该设计能够使采样效果得到明显改善,AD9226原本65MHz的采样速率提高到195MHz。

[1]王瑱,陶然,单涛.AD 9769764和高速FIFO在TMS34高4高 CTM 34高TM 34高系统中的应用[J].微计算机信息2004,20(7):80-82.

[2]王和国,张玉静,刘书明.基于AD 9516的高速四通道时间交叉采样时钟的设计[J].国外电子元器件,2008(6):7-10.

[3]齐红涛,苏涛.基于FPG A的高速A D采样设计[J].航空兵器,2010(1):35-39.

[4]卓浩泽,龚仁喜,谢玲玲,等.基于FPG A的多路高速数据采集系统的设计[J].电测与仪表,2011(9):65-68.

[5]洪萌,耿相铭.基于FPG A高速并行采样技术的研究[J].现代电子技术,2011,34(5):180-182.

[6]程耀林.高速ADC交叉采样控制器的FPG A实现[J].仪表技术与传感器,2013(1):36-39.

[7]张晨亮,苏学军,王成刚,等.基于AD 92922626的数据采集板设计与实现[J].实验技术与管理,2017,34(1):6363-6666.

Design of High Speed Cross Sampling Based on FPGA and AD9226

文章来源:《电脑与电信》 网址: http://www.dnydxzz.cn/qikandaodu/2020/0522/335.html